Xcr3064xl-7vqg100c Programmable Logic Device (CPLD / FPGA) Original Stock

describe

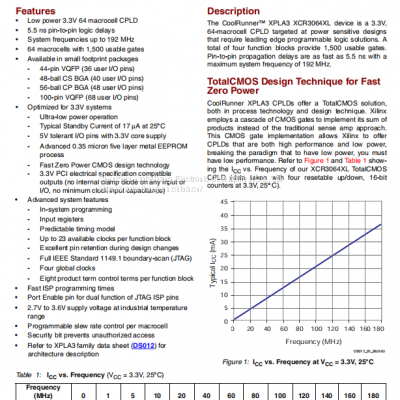

™ Xpla3xcr3064xl device is a 3.3V, 64 macro battery CPLD, which is designed for power sensitivity and requires leading programmable logic solutions. A total of 1500 doors are available. The propagation delay speed of the needle can reach 5.5ns, and the maximum system frequency is 192mhz.

Totalcmos fast zero power design technology

Coolrunner xpla3cplds provides a totalcmos solution in process technology and design technology. Xilinx uses cascaded CMOS gates to realize the sum of its products, rather than the traditional sense amplifier method. This CMOS gate implementation allows Xilinx to provide CPLD with both high performance and low power consumption, breaking the paradigm that low performance is necessary to have low power consumption. See Figure 1 and table 1, which show iccvs, respectively. Our xcr3064xltotalcmoscpld frequency (data with 4 resettable up / down, 16 bit counters at 3.3V, 25 ° C).

features

• low power 3.3V 64 macrocell CPLD

• 5.5 ns for pin logic delay

• system frequency up to 192 MHz

• 64 macro units, 1500 available doors

• small size packaging

-44 pin vqfp (36 user I / O pins)

-48 spherical CS BGA (40 user I / O pins)

-56 spherical CP BGA (48 user I / O pins)

-100 pin vqfp (68 user I / O pins)

• optimized for 3.3V systems

-Ultra low power operation

-The typical standby current at 25 ° C is 17 μ A

-5V fault tolerant I / O pin with 3.3V core power supply

-Advanced 0.35 micron five layer metal EEPROM

process

-Fast zero power CMOS Design Technology

-3.3V PCI electrical specification compatibility

Output (no internal clamping diode on any input or output)

Input / output, no minimum clock input capacitance)

• advanced system functions

-In system programming

-Input register

-Predictable time model

-Up to 23 available clocks per function block

-Maintain excellent pins during design changes

-Full IEEE standard 1149.1 boundary scan (JTAG)

-Four global clocks

-Each function block has eight product terms and control terms

• fast ISP programming

• port enable pin for JTAG ISP pin dual function

• power supply temperature from 7V to 7V

Range

• programmable conversion rate control for each macro unit

• security bits prevent unauthorized access

• refer to xpla3 series data sheet (ds012) for details

Architecture description

Send Inquiry to This Supplier

You May Also Like

-

Mt25ql128aba1ese-0sit nor Flash Memory IC AgentNegotiableMOQ: 1 Piece

-

Pic32mx330f064h-i / Pt 32-bit Microcontroller - MCU Original StockNegotiableMOQ: 1 Piece

-

Pic32mx130f064b-i / ml 32-bit Microcontroller - MCU Original StockNegotiableMOQ: 1 Piece

-

At91m55800a-33au ARM Microcontroller - MCU Original StockNegotiableMOQ: 1 Piece

-

M25p32-vmp6tg nor Flash Magnesium Original SpotNegotiableMOQ: 1 Piece

-

Tps27081addcr Has the Price Advantage of Level Displacement and Slew Rate ControlNegotiableMOQ: 1 Piece

-

Tps54202ddcr Friendly Synchronous Buck Converter in StockNegotiableMOQ: 1 Piece

-

Sn65hvd230qdrg4q1 Automotive 3.3V Can TransceiverNegotiableMOQ: 1 Piece

-

Tle2064mdr Military Grade, Four Way, 36-V, 2-MHz, in to V +, JFET Input Operational AmplifierNegotiableMOQ: 1 Piece

-

Sn65mlvd200adr LVDS Interface IC Ti Original StockNegotiableMOQ: 1 Piece